Los procesadores Intel Cannon Lake traerán las instrucciones AVX-512 a la gama domestica

Desde Anandtech nos llega el aviso sobre una actualización en los documentos que Intel entrega a los desarrolladores de software, donde informa que la compañía comenzará a presentar varias extensiones del conjunto de instrucciones AVX-512 próximamente.

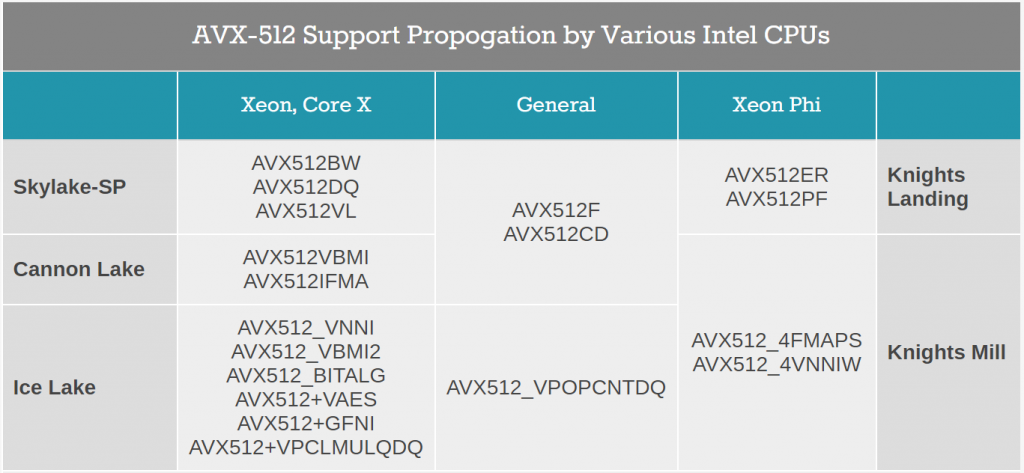

Hasta la fecha el conjunto de instrucciones AVX-512 es exclusivo de la actual gama de alto rendimiento para escritorio (HEDT) Skylake-X, y también en el sector destinado a servidores y estaciones de trabajo con los procesadores Xeon “Skylake-W” y Xeon Scalable “Skylake-SP” y en las estaciones de procesadores de alto computo escalables Xeon Phi Knights Landing y Knights Mill, viendo donde están destinadas hasta ahora las instrucciones AVX-512, nos podemos hacer una idea de su función.

Agregar este tipo de instrucciones a la gama consumo es un desarrollo importante, a pesar de que el conjunto de instrucciones se diseñó principalmente para procesar grandes cantidades de datos comunes para servidores y, hasta cierto punto, estaciones de trabajo, como codificación, renderizado, criptografía, aprendizaje profundo y estudio de la inteligencia artificial entre otros ámbitos, Intel parece interesada en llevar estos conjuntos de instrucciones de alto rendimiento a los usuarios comunes por algún motivo.

Con la actualización del documento se espera la llegada de las instrucciones AVX -512 en la gama domestica (mainstream/MSDT) con el lanzamiento de los procesadores Cannon Lake, con nombre en código (CNL) e Ice Lake (ICL), los primeros procesadores de la compañía fabricados a 10 nm, y que tanto se están haciendo de esperar, pues en un principio su lanzamiento se tenía previsto para el presente año, retrasándose hasta un fecha todavía por confirmar durante el próximo año 2018.

En un principio la llegada de Cannon Lake e Ice Lake solo iban a suponer un cambio en el proceso de fabricación a 10 nm sobre Coffee Lake, manteniendo los 8 núcleos / 16 hilos, y con nuevos conjuntos de instrucciones, pero la implementación del soporte para instrucciones AVX-512 requiere de un gran ancho de banda y de más tamaño, del que disponen los procesadores Skylake-X/SP con una gran cantidad de memoria caché y varias controladoras de memoria, aunque hay que matizar que actualmente los procesadores de 6 y 8 núcleos Skylake-X solo tienen un puerto FMA disponible para el soporte AVX-512-F, pero los chips a partir de 10 núcleos tienen los dos puertos FMA habilitados para AVX-512-F, lo que se traduce en el doble de rendimiento teórico, por lo que todavía queda por ver como se implementara en los procesadores Coffee Lake e Ice Lake.

De momento según el informe, los procesadores Cannon Lake admitirán AVX512F, AVX512CD, AVX512DQ, AVX512BW y AVX512V, equiparándose a los actuales Skylake-SP, además se espera que también admita los comandos AVX512_IFMA y AVX512_VBMI, aunque todavía por confirmar si se limitara a la gama servidor o se extenderá a la gama doméstica.

Los procesadores Ice Lake de Intel admitirán AVX512_VPOPCNTDQ, equiparándose a los Xeon Phi ‘Knights Mill’, así como instrucciones AVX512_VNNI, AVX512_VBMI2, AVX512 + VPCLMULQDQ y AVX512_BITALG junto a los algoritmos AES y GFNI conocidos para la encriptación y corrección de errores AVX512 + VAES y AVX512 + GFNI.

También cabe recordar que las instrucciones AVX-2 que encontramos en los procesadores Coffee Lake reducen la velocidad del procesador en los modo Turbo para mantener la estabilidad cuando se hacen uso de ellas, por lo que todavía queda por ver cómo van a afectar las instrucciones AVX-512 a la velocidad Turbo a partir de ahora en los procesadores de la gama doméstica.

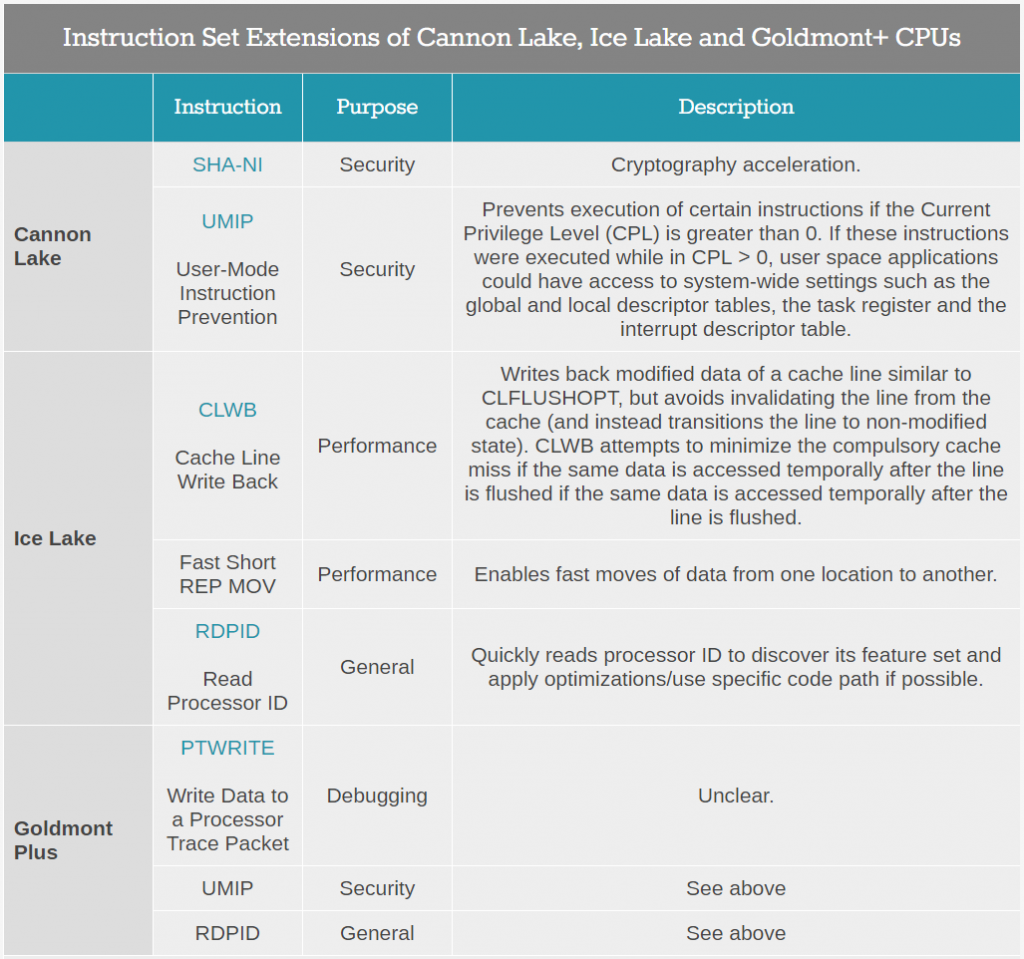

Además de estas instrucciones AVX-512, también se espera la llegada de otras nuevas aparte y que os mostramos en el siguiente gráfico.

Vía: Techpowerup

Y vosotr@s que opináis con este movimiento, ¿se avecinan cambios importantes en la adopción de instrucciones AVX para el ámbito común? ¿o se trata de una transición para convertir la actual gama HEDT en la MSDT de consumo? Nos interesan vuestras opiniones.